|

|

|

|

|

||

|

Title of the Talk |

: |

Mobile Phones and Multicores: Programming Nightmare or Architectural Renaissance | |

|

Speaker |

: |

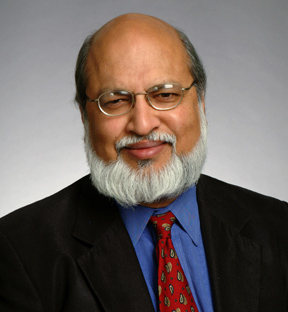

Arvind,

Johnson

Professor of Computer Science and Engineering,Computer

Science and Artificial Intelligence laboratory, Massachusetts

Institute of Technology

Arvind received his B.Tech degree in electrical engineering at Indian Institute of Technology, Kanpur, India, in 1969. He attended graduate school in computer science at the University of Minnesota, Minneapolis and received M.S. and Ph.D. degrees in 1972 and 1973, respectively. He was Assistant Professor of Computer Science in the University of California, Irvine from 1974-1978. After that he joint the EECS faculty at MIT as an Assistant Professor where is currently the Johnson Professor of Computer Science and Engineering. Arvind’s group, in collaboration with Motorola, built the Monsoon dataflow machines and its associated software in the late eighties. In 2000, Arvind started Sandburst which was sold to Broadcom in 2006. In 2003, Arvind co-founded Bluespec Inc., an EDA company to produce a set of tools for high-level synthesis. In 2001, Dr. R. S. Nikhil and Arvind published the book "Implicit parallel programming in pH". Arvind's current research focus is on enabling rapid development of embedded systems. Arvind is a Fellow of IEEE and ACM, and a member of the National Academy of Engineering. |

|

|

Abstract |

: |

In the developing world a mobile phone is the only computer most people have. With countries like India getting seven million new mobile phone customers per month, mobile devices and the associated services infrastructure are going to be the main drivers for both industry and research. In this new world, power and cost constraints completely determine functionality. Meeting power and cost constraints for mobile devices and sensors is much easier through dedicated chips than via software programmability. This vision is counter to the steadily decreasing new chip-starts in industry driven by rising chip development costs. A fundamental shift is needed in the current design flow of systems-on-a-chip (SoCs) to fulfill this demand in a cost-efficient manner. We will present a method of designing systems that facilitates synthesis of complex SoCs from reusable “IP” modules. The technical challenge is to provide a method for connecting modules in a parallel setting so that the functionality and the performance of the composite are predictable. |

|

A-10, Sector 62, Noida-201307, Uttar Pradesh, India

Copyright © 2007 All Rights Reserved.